# **Developers Workshop**

## August 13-14, 2009 Stanford, CA

http://NetFPGA.org/DevWorkshop

*Copyright* © 2009 by respective authors Unlimited rights to distribute this work is permitted.

- Program Chairs

- John W. Lockwood: Stanford University

- Andrew W. Moore: Cambridge University

- Program Committee

- Satnam Singh, Microsoft Research Cambridge

- David Miller, Cambridge University Computer Laboratory

- Gordon Brebner, Xilinx

- Martin Žádník, Brno University of Technology

- Glen Gibb: Stanford University

- Adam Covington: Stanford University

- David Greaves: Cambridge University

- Eric Keller: Princeton University

- NetFPGA Sponsors

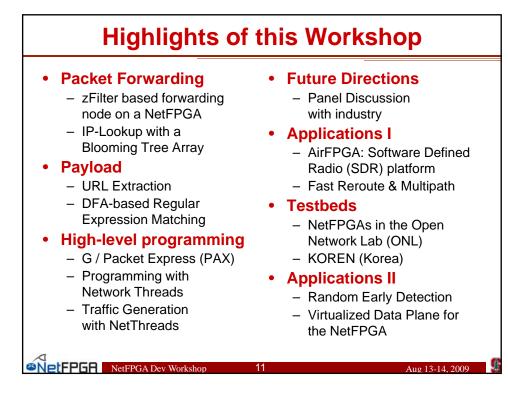

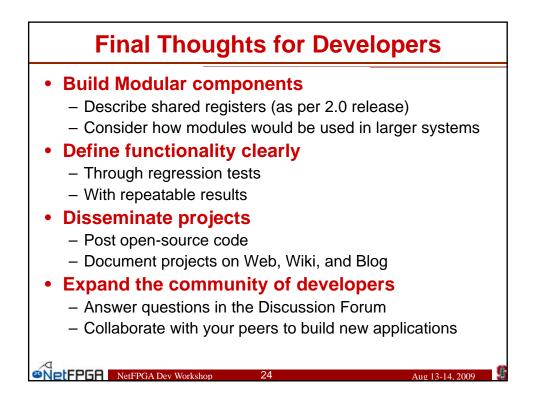

## Welcome from the Program Chairs

- <u>State of the NetFPGA Program</u>

- John W. Lockwood (Stanford University) (Slides) pp. 5-16

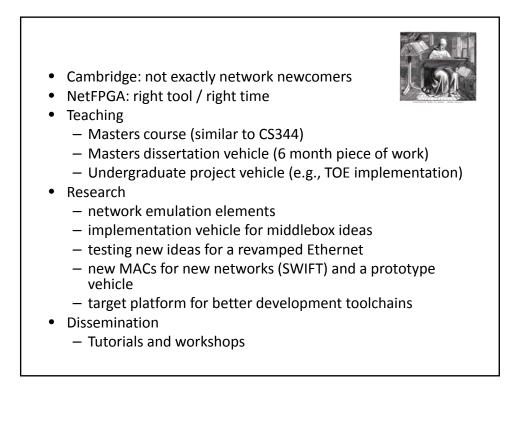

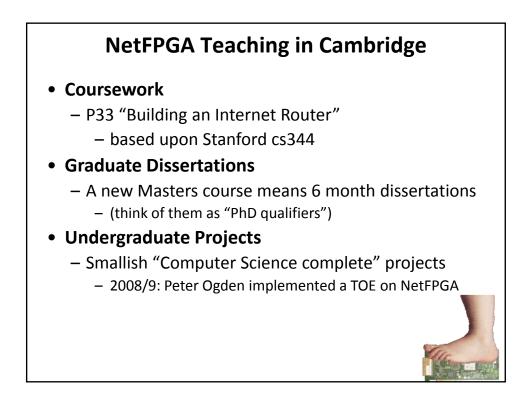

- NetFPGA at Cambridge

- Andrew W. Moore (University of Cambridge) (Slides) pp. 17-23

## Session 1: Packet Forwarding

- <u>zFilter Sprouter Implementing zFilter based forwarding node on a NetFPGA</u>

- o J. Keinänen, P. Jokela, K. Slavov (Ericsson Research)

- (Wiki) and (Paper) pp. 24-31

- <u>IP-Lookup with a Blooming Tree Array</u>

- Gianni Antichi, Andrea Di Pietro, Domenico Ficara, Stefano Giordano, Gregorio Procissi, Cristian Vairo, Fabio Vitucci (University of Pisa)

- (Wiki) and (Paper) pp. 32-38

## Session 2: Payload Processing

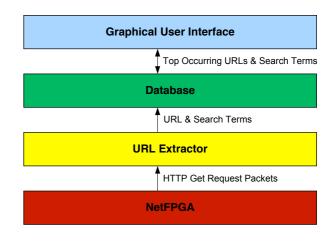

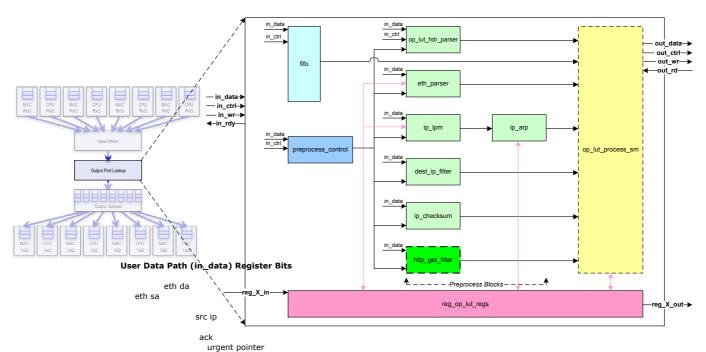

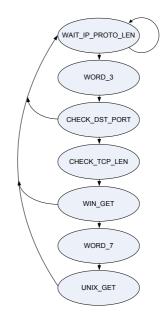

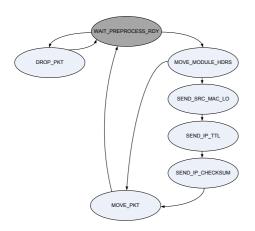

URL Extraction

0

- o M. Ciesla, V. Sivaraman, A. Seneviratne (UNSW, NICTA)

- (Wiki) and (Paper) and (Slides) pp. 39-44

- DFA-based Regular Expression Matching Engine on NetFPGA

- o Y. Luo, S. Li, Y. Liu (University of Massachusetts Lowell)

- (Wiki) and (Paper) pp. 45-49

## Session 3: High-Level Programming

- High-level programming of the FPGA on NetFPGA

- M. Attig, G. Brebner (Xilinx)

- (Wiki) and (Paper) pp. 50-55

- NetThreads: Programming NetFPGA with Threaded Software

- M. Labrecque, J. Steffan, G. Salmon, M. Ghobadi, Y. Ganjali (University of Toronto) • (Wiki) and (Paper) and (Slides) pp. 56-61

- <u>NetFPGA-based Precise Traffic Generation</u>

- G. Salmon, M. Ghobadi, Y. Ganjali, M. Labrecque, J. Steffan (University of Toronto)

(Wiki), (Paper) and (Slides) pp. 62-68

## Session 4: Applications I

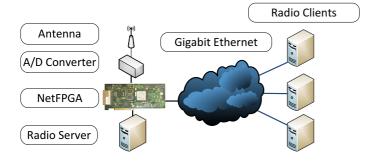

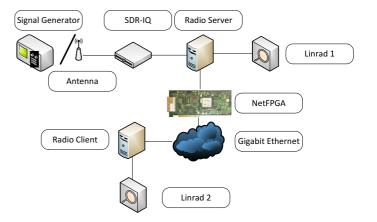

- AirFPGA: A software defined radio platform based on NetFPGA

- James Zeng, Adam Covington, and John Lockwood (Stanford University); Alex Tutor (Agilent)

- (Wiki), (Paper), and (Slides) pp. 69-75

- Fast Reroute and Multipath

- Mario Flajslik, Nekhil Handigol, James Zeng (Stanford University- CS344 Project)

- (Wiki) and (Paper) pp. 76-79

## Session 5: Testbeds

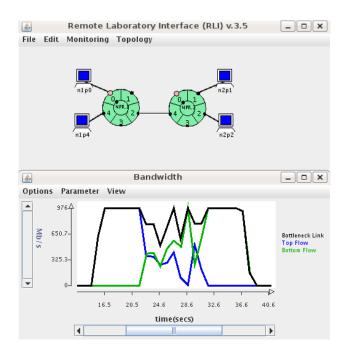

- <u>NetFPGAs in the Open Network Lab (ONL)</u>

- Charlie Wiseman, Jonathan Turner, John DeHart, Jyoti, Parwatikar, Ken Wong, David Zar (Washington University in St. Louis)

- (Wiki), (Paper), and (Slides) pp. 80-85

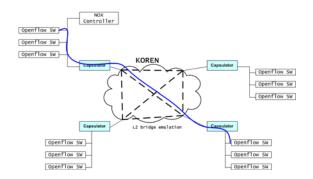

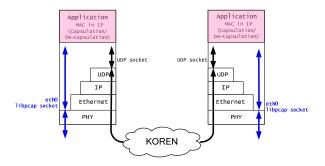

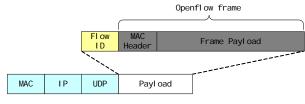

- Implementation of a Future Internet Testbed on KOREN based on NetFPGA/OpenFlow Switches

- Man Kyu Park, Jae Yong Lee, Byung Chul Kim, Dae Young Kim (Chungnam National University)

- (Wiki) and (Paper) pp. 86-89

## Session 6: Applications II

- <u>RED Random Early Detection</u>

- Gustav Rydstedt and Jingyang Xue (Stanford University - CS344 Project)

- <u>(Wiki)</u>

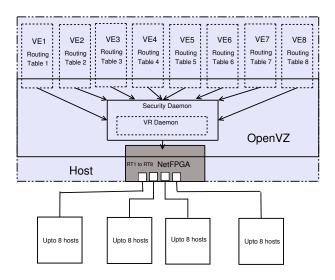

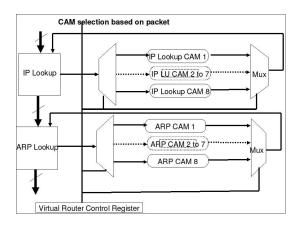

- <u>A Fast, Virtualized Data Plane for the NetFPGA</u>

- M. Anwer, N. Feamster (Georgia Institute of Technology)

- (Wiki) and (Paper) pp. 90-94

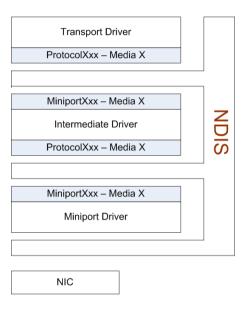

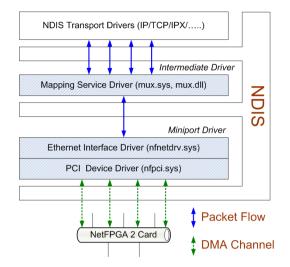

- <u>A Windows Support Framework for the NetFPGA 2 Platform</u>

- o C. Tian, D. Zhang, G. Lu, Y. Shi, C. Guo, Y. Zhang

- (Wiki) and (Paper) 95-101

## Photographs from the event

Participants at the NetFPGA Developers Workshop on August 13, 2009 at Stanford University

Live Demonstrations

| oject (Title & Summary)          | Base  | <u>Status</u> | Organization             | Docs.        |

|----------------------------------|-------|---------------|--------------------------|--------------|

| v4 Reference Router              | 2.0   | Functional    | Stanford University      | <u>Guide</u> |

| Quad-Port Gigabit NIC            | 2.0   | Functional    | Stanford University      | <u>Guide</u> |

| thernet Switch                   | 2.0   | Functional    | Stanford University      | <u>Guide</u> |

| ardware-Accelerated Linux Router | 2.0   | Functional    | Stanford University      | Guide        |

| acket Generator                  | 2.0   | Functional    | Stanford University      | Wiki         |

| OpenFlow Switch                  | 2.0   | Functional    | Stanford University      | Wiki         |

| DRAM-Router                      | 2.0   | Functional    | Stanford University      | Wiki         |

| NetFlow Probe                    | 1.2   | Functional    | Brno University          | Wiki         |

| AirFPGA                          | 2.0   | Functional    | Stanford University      | Wiki         |

| Fast Reroute & Multipath Router  | 2.0   | Functional    | Stanford University      | Wiki         |

| letThreads                       | 1.2.5 | Functional    | University of Toronto    | Wiki         |

| JRL Extraction                   | 2.0   | Functional    | Univ. of New South Wales | Wiki         |

| Filter Sprouter (Pub/Sub)        | 1.2   | Functional    | Ericsson                 | Wiki         |

| Windows Driver                   | 2.0   | Functional    | Microsoft Research       | Wiki         |

| P Lookup w/Blooming Tree         | 1.2.5 | In Progress   | University of Pisa       | Wiki         |

| DFA                              | 2.0   | In Progress   | UMass Lowell             | Wiki         |

| G/PaX                            | ?.?   | In Progress   | Xilinx                   | Wiki         |

| Precise Traffic Generator        | 1.2.5 | In Progress   | University of Toronto    | Wiki         |

| Open Network Lab                 | 2.0   | In Progress   | Washington University    | Wiki         |

| KOREN Testbed                    | ?.?   | In Progress   | Chungnam-Korea           | Wiki         |

| RED                              | 2.0   | In Progress   | Stanford University      | Wiki         |

| /irtual Data Plane               | 1.2   | In Progress   | Georgia Tech             | Wiki         |

| Precise Time Protocol (PTP)      | 2.0   | In Progress   | Stanford University      | Wiki         |

| Deficit Round Robin (DRR)        | 1.2   | Repackage     | Stanford University      | Wiki         |

| How might VOLLUC                                                                          | $\sim N_{O} + EDC \Lambda^{2}$                                         |

|-------------------------------------------------------------------------------------------|------------------------------------------------------------------------|

| How might YOU us                                                                          | e Netrrua!                                                             |

| Build an accurate, fast, line-rate NetDummy/nistnet element                               | Hardware channel bonding reference implementation                      |

| A flexible home-grown monitoring card                                                     | TCP sanitizer                                                          |

| Evaluate new packet classifiers                                                           | Other protocol sanitizer (applications UDP DCCP, etc.)                 |

| <ul> <li>(and application classifiers, and other neat network apps)</li> </ul>            | Full and complete Crypto NIC                                           |

| Prototype a full line-rate next-generation Ethernet-type                                  | IPSec endpoint/ VPN appliance                                          |

| Trying any of Jon Crowcrofts' ideas (Sourceless IP routing for example)                   | VLAN reference implementation                                          |

| Demonstrate the wonders of Metarouting in a different implementation (dedicated hardware) | metarouting implementation                                             |

| Provable hardware (using a C# implementation and kiwi with NetFPGA as target h/w) .       | virtual <pick-something></pick-something>                              |

| Hardware supporting Virtual Routers .                                                     | intelligent proxy                                                      |

| Check that some brave new idea actually works                                             | application embargo-er                                                 |

| e.g. Rate Control Protocol (RCP), Multipath TCP,                                          | Layer-4 gateway                                                        |

| toolkit for hardware hashing                                                              | h/w gateway for VoIP/SIP/skype                                         |

| MOOSE implementation                                                                      | h/w gateway for video conference spaces                                |

| IP address anonymization                                                                  | security pattern/rules matching                                        |

| SSL decoding "bump in the wire"                                                           | Anti-spoof traceback implementations (e.g. BBN stuff)                  |

| Xen specialist nic                                                                        | IPtv multicast controller                                              |

| computational co-processor                                                                | Intelligent IP-enabled device controller (e.g. IP cameras or IP powern |

| Distributed computational co-processor                                                    | DES breaker                                                            |

| IPv6 anything                                                                             | platform for flexible NIC API evaluations                              |

| IPv6 – IPv4 gateway (6in4, 4in6, 6over4, 4over6,)                                         | snmp statistics reference implementation                               |

| Netflow v9 reference                                                                      | sflow (hp) reference implementation                                    |

| PSAMP reference                                                                           | trajectory sampling (reference implementation)                         |

| IPFIX reference                                                                           | implementation of zeroconf/netconf configuration language for rout     |

| Different driver/buffer interfaces (e.g. PFRING)                                          | h/w openflow and (simple) NOX controller in one                        |

| or "escalators" (from gridprobe) for faster network monitors                              | Network RAID (multicast TCP with redundancy)                           |

| Firewall reference                                                                        | inline compression                                                     |

| GPS packet-timestamp things                                                               | hardware accelorator for TOR                                           |

| High-Speed Host Bus Adapter reference implementations                                     | load-balancer                                                          |

| - Infiniband                                                                              | openflow with (netflow, ACL,)                                          |

| – iSCSI<br>– Myranet                                                                      | reference NAT device                                                   |

| - Fiber Channel                                                                           | active measurement kit                                                 |

| Smart Disk adapter (presuming a direct-disk interface)                                    | network discovery tool                                                 |

| Software Defined Radio (SDR) directly on the FPGA (probably UWB only)                     | passive performance measurement                                        |

| Routing accelerator                                                                       | active sender control (e.g. performance feedback fed to endpoints for  |

| - Hardware route-reflector                                                                | Prototype platform for NON-Ethernet or near-Ethernet MACs              |

| <ul> <li>Internet exchange route accelerator</li> </ul>                                   | <ul> <li>Optical LAN (no buffers)</li> </ul>                           |

## Implementing zFilter based forwarding node on a NetFPGA

Jari Keinänen, Petri Jokela, Kristian Slavov Ericsson Research, NomadicLab 02420 Jorvas, Finland firstname.secondname@ericsson.com

## ABSTRACT

Our previous work has produced a novel, Bloom-filter based, forwarding fabric, suitable for large-scale topic-based publish/subscribe [8]. Due to very simple forwarding decisions and small forwarding tables, the fabric may be more efficient than the currently used ones. In this paper, we describe the NetFPGA based forwarding node implementation for this new, IP-less, forwarding fabric. The implementation requires removing the traditional IP forwarding implementation, and replacing it with the Bloom-filter matching techniques for making the forwarding decisions. To complete the work, we provide measurement results to verify the forwarding efficiency of the proposed forwarding system and we compare these results to the measurements from the original, IP-based forwarding, implementation.

## 1. INTRODUCTION

While network-level IP multicast was proposed almost two decades ago [5], its success has been limited due to the lack of wide scale deployment. As a consequence, various forms of application-level multicast have gained in popularity, but their scalability and efficiency have been limited. Hence, a challenge is how to build a multicast infrastructure that can scale to, and tolerate the failure modes of, the general Internet, while achieving low latency and efficient use of resources.

In [8], we propose a novel multicast forwarding fabric. The mechanism is based on identifying links instead of nodes and uses in-packet Bloom filters [2] to encode source-route-style forwarding information in the packet header. The forwarding decisions are simple and the forwarding tables fairly small, potentially allowing faster, smaller, and more energy-efficient switches than what today's switches are. The proposed (inter-)networking model aims towards balancing the state between the packet headers and the network nodes, allowing both stateless and stateful operations [16].

The presented method takes advantage of "inverting" the Bloom filter thinking [3]. Instead of maintaining Bloom filters at the network nodes and verifying from incoming packets if they are included in the filter or not, we put the Bloom filters themselves in the packets and allow the nodes on the path to determine which outgoing links the packet should be forwarded to.

In this paper, we present the implementation of a forwarding node on a NetFPGA. At the first stage, we have implemented the basic forwarding node functions enabling packet delivery through the network using the described forwarding mechanism. At the same time we have been developing a FreeBSD-based end-host implementation, based on publish/subscribe networking architecture, described in [8]. The end-host implements the packet management, as well as networking related functions. The present environment supports only simple networks, but once the first release of the end-host implementation is ready, larger scale networks can be created and tested.

We selected NetFPGA as the forwarding node platform because it offers a fast way to develop custom routers. It provides a way easy to move implementations directly on hardware by taking advantage of reprogrammable FPGA circuits enabling prototype implementations that can handle high speed data transmission (1Gbps/link). We can also avoid time consuming and expensive process of designing new physical hardware components.

The rest of this paper is organized as follows. First, in Section 2, we discuss the general concepts and architecture of our solution. In Section 3, we go into details of the implementation. Next, in Section 4, we provide some evaluation and analysis of our forwarding fabric Section 5 contrasts our work with related work, and Section 6 concludes the paper.

## 2. ARCHITECTURE

Our main focus in this paper is on describing the forwarding node implementation of the Bloom-filter based forwarding mechanism referred to as zFilters. In this section, we describe the basic zFilter operations, and for more detailed description, we refer to [8].

#### 2.1 Forwarding on Bloomed link identifiers

The forwarding mechanism described in this paper

is based on identifying links instead of nodes. In the basic operation, the forwarding nodes do not need to maintain any state other than a Link ID per interface. The forwarding information is constructed using these Link IDs and including them in the packet header in a Bloom filter fashion. For better scalability, we introduce an enhancement that inserts a small amount of state in the network by creating virtual trees in the network and identifying them using similar identifiers as the Link IDs. In this section we describe the basics of such forwarding system, and more detailed information can be found from [8].

### 2.1.1 The basic Bloom-filter-based forwarding

For each point-to-point link, we assign two identifiers, called Link IDs, one in each direction. For example, a link between the nodes A and B has two identifiers,  $\overrightarrow{AB}$  and  $\overleftarrow{AB}$ . In the case of a multi-point link, such as a wireless link, we consider each pair of nodes as a separate link. With this setup, we don't need any common agreement between the nodes on the link identities – each link identity may be locally assigned, as long as the probability of duplicates is low enough.

Basically, a Link ID is an *m*-bit long name with just k bits set to one. In [8] we discuss the proper values for m and k, and what are the consequences if we change the values; however, for now it is sufficient to note that typically  $k \ll m$  and m is relatively large, making the Link IDs statistically unique (e.g., with m = 248, k = 5, # of Link IDs  $\approx m!/(m-k)! \approx 9 * 10^{11}$ ).

The complete architecture includes a management system that creates a graph of the network using Link IDs and connectivity information, without any dependency on end-point naming or addressing (creating the "topology map" or "routing table"). Using the network graph, the topology system can determine a forwarding tree for any publication, from the locations of the publisher and subscribers [16]. In this paper, however, we assume that such topology management exists and refer to [8] for more detailed discussion about the complete architecture.

When the topology system gets a request to determine a forwarding tree for a certain publication, it first creates a conceptual delivery tree for the publication using the network graph. Once it has such an internal representation of the tree, it knows which links the packets need to pass, and it can determine when to use Bloom filters and when to create state. [16]

In the default case, we use a source-routing based approach which makes forwarding independent from routing. Basically, we encode all Link IDs of the delivery tree into a Bloom filter, forming the forwarding zFilter for the data. Once all Link IDs have been added to the filter, a mapping from the data topic identifier to the zFilter is given to the node acting as the data

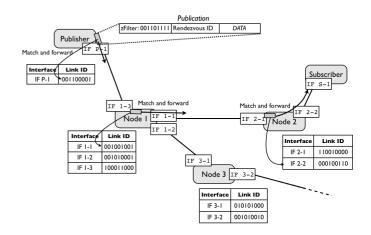

Figure 1: Example of Link IDs assigned for links, as well as a publication with a zFilter, built for forwarding the packet from the Publisher to the Subscriber.

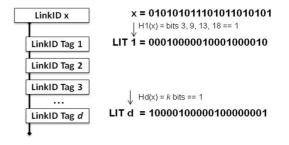

Figure 2: An example relation of one Link ID to the d LITs, using k hashes on the Link ID.

source, which now can create packets that will be delivered along the tree.

Each forwarding node acts on packets roughly as follows. For each link, the outgoing Link ID is ANDed with the zFilter found in the packet. If the result matches with the Link ID, it is assumed that the Link ID has been added to the zFilter and that the packet needs to be forwarded along that link.

With Bloom filters, matching may result with some false positives. In such a case, the packet is forwarded along a link that was not added to the zFilter, causing extra traffic. While the ratio of false positives depends on the number of entries added to the filter, we get a practical limit on how many link names can be included into a single zFilter.

Our approach to the Bloom filter capacity limit is twofold: Firstly, we use recursive layering [4] to divide the network into suitably-sized components and secondly, the topology system may dynamically add *virtual links* to the system (see Section 2.2.1).

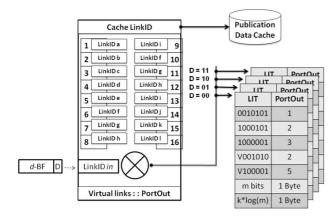

Figure 3: Outgoing interfaces are equipped with d forwarding tables, indexed by the value in the incoming packet.

#### 2.1.2 Link IDs and LITs

To reduce the number of false positives, we introduced [8] Link ID Tags (LITs), as an addition to the plain Link IDs. The idea is that instead of each link being identified with a single Link ID, every unidirectional link is associated with a set of d distinct LITs (Fig. 2). This allows us to construct zFilters that can be optimized, e.g., in terms of the false positive rate, compliance with network policies, or multi path selection. The approach allows us to construct different candidate zFilters and to to select the best-performing Bloom filter from the candidates, according to any appropriate metric.

The forwarding information is stored in the form of d forwarding tables, each containing the LIT entries of the active Link IDs, as depicted in Fig. 3. The only modification of the base forwarding method is that the node needs to be able to determine which forwarding table it should perform the matching operations; for this, we include the index in the packet header before zFilter.

The construction of the forwarding Bloom filter is similar to the one discussed in single Link ID case, except that for the selected path from the publisher to the subscriber, we calculate d candidate filters, one using each of the d values, which are each equivalent representations of the delivery tree.

As a consequence, having d different candidates each representing the given delivery tree is a way to minimise the number of false forwardings in the network, as well as restricting these events to places where their negative effects are smallest. [8]

## 2.2 Stateful operations

In the previous, we presented the basic, single link, based forwarding solution. A forwarding node does not maintain any connection or tree based states, the only information that it has to maintain is the outgoing Link IDs. In this section, we discuss some issues that enhance the operation with the cost of adding small amount of state on the forwarding nodes.

## 2.2.1 Virtual links

As discussed in [8], the forwarding system in its basic form, is scalable into metropolitan area networks with sparse multicast trees. However, in case of dense multicast trees and larger networks, increasing the number of Link IDs in the Bloom filter will increase the number of false positives on the path. For more efficient operations, the topology layer can identify different kinds of delivery trees in the network and assign them virtual Link IDs that look similar to Link IDs described earlier.

Once a virtual link has been created, each participating router is configured with the newly created virtual Link ID information, adding a small amount of state in its forwarding table. The virtual link identifier can then be used to replace all the single Link IDs needed to form the delivery tree, when creating zFilters.

### 2.2.2 Link failures - fast recovery

All source routing based forwarding mechanisms are vulnerable when link failures occur in the network. While the packet header contains the exact route, the packets will not be re-routed using other paths.

In zFilters [8], we have proposed two simple solutions for this mentioned problem: we can use either pre-configured virtual links, having the same Link ID as the path which it is replacing or then we can use pre-computed zFilters, bypassing the broken link. The former method requires an additional signalling message so that the alternative path is activated, but the data packets can still use the same zFilter and do not need any modifications. The latter solutions requires that the alternative path is added to the zFilter in the packet header, thus increasing the fill factor of the zFilter, increasing the probability of false positives. However, the solution does not require any signalling when the new path is needed.

### 2.2.3 Loop prevention

The possibility for false positives means that there is a risk for loops in the network. The loop avoidance has also been discussed in [8] with some initial mechanisms for avoiding such loops. Locally, it is possible to calculate zFilter that do not contain loops, but when the packet is passed to another administrative domain, it is not necessarily possible. One other alternative is to use TTL-like field in the packet for removing looping packets. Work is going on in this area.

## 2.3 Control messages, slow path, and services

To inject packets to the slow path on forwarding nodes, each node can be equipped with a local, unique Link ID denoting the node-internal passway from the switching fabric to the control processor. That allows targeted control messages that are passed only to one or a few nodes. Additionally, there may a be virtual Link ID attached to these node-local passways, making it possible to multicast control messages to a number of forwarding nodes without needing to explicitly name each of them.

By default such control messages would be simultaneously passed to the slow path and forwarded to the neighboring nodes. The simultaneous forwarding can be blocked easily, either by using zFilters constructed for node-to-node communication, or using a virtual Link ID that is both configured to pass messages to the slow path and to block them at all the outgoing links.

Generalising, we make the observation that the egress points of a virtual link can be basically anything: nodes, processor cards within nodes, or even specific services. This allows our approach to be extended to upper layers, beyond forwarding, if so desired.

## 3. IMPLEMENTATION

In the project, we have designed a publish/subscribe based networking architecture with a novel forwarding mechanism. The motivation to choose NetFPGA as the platform for our forwarding node implementation was based on our requirements. We needed a platform that was capable for high data rates and has the flexibility that allows implementation of a completely new forwarding functionality.

The current implementation has roughly 500 lines of Verilog code, and it implements most of the functions described in the previous section. In this section, we will go deeper in the implementation and describe what changes we have made to the original reference implementation.

#### 3.1 Basic forwarding method

| Algorithm 1: Forwarding method of LIPSIN                                                                                                    |

|---------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Input</b> : Link IDs of the outgoing links; zFilter in the packet header                                                                 |

| for each Link ID of outgoing interface do<br>if zFilter $\mathcal{C}$ Link ID == Link ID then<br>  Forward packet on the link<br>end<br>end |

The core operation of our forwarding node is to make the forwarding decision for incoming packets. With zFilters, the decision is based on a binary AND and comparison operations, both of which are very simple to implement in hardware. The forwarding decision

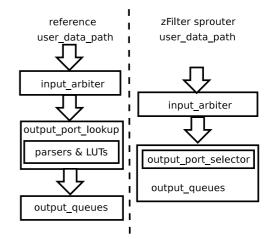

Figure 4: Reference and modified datapaths

(Alg. 1) can be easily parallelized, as there are no memory or other shared resource bottlenecks. The rest of this section describes the implementation based on this simple forwarding operation.

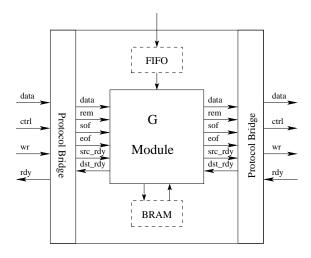

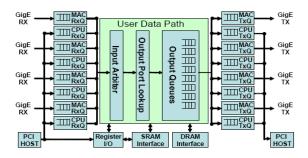

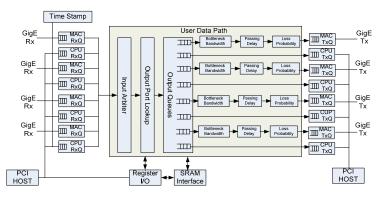

## 3.2 Forwarding node

For the implementation work we identified all unnecessary parts from the reference switch implementation and removed most of the code that is not required in our system (Figure 4). The removed parts were replaced with a simple zFilter switch.

The current version implements both the LIT and the virtual link extensions, and it has been tested with four real and four virtual LITs per each of the four interface. We are using our own *EtherType* for identifying zFilter packets. The implementation drops incoming packets with wrong ethertype, invalid zFilter, or if the TTL value has decreased down to zero.

The *output\_port\_lookup* module and all modules related to that are removed from the reference switch design. The zFilter implementation is not using any functions from those modules.

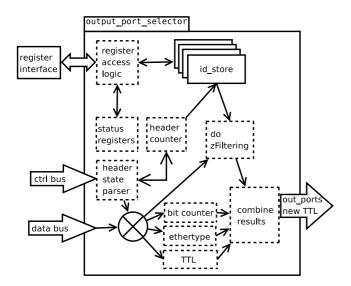

Our prototype has been implemented mainly in the new *output\_port\_selector* module. This module is responsible for the zFilter matching operations, including binary AND operation between the LIT and zFilter, and comparing the result with the LIT, as well as placing the packets to the correct output queues based on the matching result. The new module is added in *output\_queueus*. Detailed structure of the *output\_port\_selector* module is shown in Figure 5.

#### 3.2.1 Packet forwarding operations

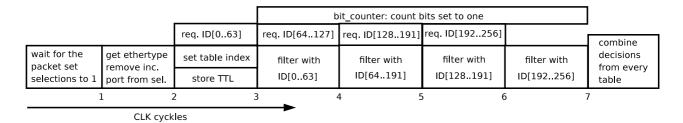

All incoming data is forwarded, straight from the input arbiter, to the *store\_packet* module, that stores it into the SRAM and to the *output\_port\_selector* mod-

Figure 5: Structure of the output port selector module

ule for processing. Packets arrive in 64-bit pieces, one piece on each clock cycle. The packet handling starts with initiating processing for different verifications on the packet as well as on the actual zFilter matching operation.

The incoming packet processing takes place in various functions, where different kinds of verifications are performed to the packet. The three parallelized verification operations, *bit\_counter*, *ethertype*, and *TTL*, make sanity checks on the packet, while the *do zFiltering* makes the actual forwarding decisions. In practice, for enabling parallelization, there exists separate instances of logic blocks that do zFiltering, one for each of the Link IDs (both for ordinary and virtual links). In the following, we go through the functions in Figure 5 function-by-function and in Figure 6, the operations are shown in function of clock cycles.

In do zFiltering, we make the actual zFilter matching for each 64-bit chunk. First, we select the correct LITs of each of the interfaces based on the d-value in the incoming zFilter. For maintaining the forwarding decision status for each of the interfaces during the matching process, we have a bit-vector where each of the interfaces has a single bit assigned, indicating the final forwarding decision. Prior to matching process, all the bits are set to one. During the zFilter matching, when the system notices that there is a mismatch in the comparison between the AND-operation result and the LIT, the corresponding interface's bit in the bit-vector is set to zero.

Finally, when the whole zFilter has been matched with the corresponding LITs, we know the interfaces where the packet should be forwarded by checking from the bit-vector, which of the bits are still ones. While the forwarding decision is also based on the other verifications on the packet, the *combine results* collects the information from the three verification functions in addition to the zFilter matching results. If all the collected verification function results indicate positive forwarding decision, the packet will be put to all outgoing queues indicated by the bit vector. The detailed operations of the verification functions are described in 3.2.2.

#### 3.2.2 Support blocks and operations

To avoid the obvious attack of setting all bits to one in the zFilter, and delivering the packet to all possible nodes in the network, we have implemented a very simple verification on the zFilter. We have limited the maximum number of bits set to one in a zFilter to a constant value, which is configurable from the user space; if there are more bits set to one than the set maximum value, the packet is dropped. The bit counting function calculates the number of ones in a single zFilter and it is implemented in the *bit\_counter* module. This module takes 64 bits wide input and it returns the amount of ones on the given input. Only wires and logic elements are used to calculate the result and there are no registers inside, meaning that block initiating the operation should take care of the needed synchronization.

The *Ethertype* of the packet is checked upon arrival. At the moment, we are using 0xacdc as the ethertype, identifying the zFilter-based packets. However, in a pure zFilter based network, the ethernet is not necessarily needed, thus this operation will be obsolete. The third packet checking operation is the verification of the TTL. This is used in the current implementation to avoid loops in the network. This is not an optimal solution for loop prevention, and better solutions are currently being worked on.

The *id\_store* module implements Dual-Port RAM functionality making it possible for two processes to access it simultaneously. This allows modifications to LIT:s without blocking forwarding functionality. The *id\_store* module is written so that it can be synthesized by using either logic cells or BRAM (Block RAM). One of the ports is 64 bits wide with only read access and it is used exclusively to get IDs for zFiltering logic. There is one instance of the *id\_store* module for each LIT and virtual LIT. This way the memory is distributed and each instance of the filtering logic have access to *id\_store* at line rate. The other port of the *id\_store* module is 32 bits wide with a read and write connection for the user space access. This port is used by the management software (cf. Section 3.2.3) to configure LIT:s on the interfaces. One new register block is reserved for this access.

One additional register block is added for module control and debug purposes. It is used to read information that is collected into the status registers during forwarding operations. Status registers contain constants,

Figure 6: Dataflow diagram

amount of links, maximum amount of LITs and virtual LITs per link and also the LIT length. In addition, information about the last forwarded packet is stored together with the result of the bit count operation, d, TTL, and incoming port information. This block is also used to set the maximum amount of ones allowed in a valid zFilter.

### 3.2.3 Management software

For configuration and testing purposes, we have developed a specialized management software. When the system is started, the management software is used to retrieve information from the card and, if needed, to configure new values on the card. The information that the software can handle, includes the length of the LITs, the maximum d value describing the number of LITs used, as well as both link and virtual link information from each of the interfaces.

Internally, the software works by creating chains of commands that it sends in batch to the hardware, gets the result and processes the received information. The commands are parsed using specific, for the purpose generated, grammar. The parsing is done using byacc and flex tools, and is therefore easily extendable.

For testing purposes, the software can be instructed to send customizable packets to the NetFPGA card, and to collect information about the made forwarding decisions. The software supports the following features:

- Selecting the outgoing interface

- Customizing the delay between transmitted packets

- Varying the sizes of packets

- Defining the Time-to-live (TTL) field in packet header

- Defining the d value in packet header

- Defining the zFilter in the packet header

- Defining the ethernet protocol field

| # of     | Average    | Std.     | Latency/ |

|----------|------------|----------|----------|

| NetFPGAs | latency    | Dev.     | NetFPGA  |

| 0        | $16 \mu s$ | $1\mu s$ | N/A      |

| 1        | $19 \mu s$ | $2\mu s$ | $3\mu s$ |

| 2        | $21 \mu s$ | $2\mu s$ | $3\mu s$ |

| 3        | $24\mu s$  | $2\mu s$ | $3\mu s$ |

Table 1: Simple latency measurement results

## 4. EVALUATION

The basic functionality is tested by running simple scripts that use control software (cf. Section 3.2.3) to set Link IDs and to generate and send traffic. In practise, two network interfaces of the test host are connected to the NetFPGA of which one is used to send packets to the NetFPGA and the other one to receive forwarded packets. Forwarding decisions are also followed by tracking status registers. The results of the tests show that the basic forwarding functions work on the NetFPGA, also when using LITs. In addition, the packet verification operations, counting set bits, TTL verification, as well as ethertype checking were working as expected.

## 4.1 Performance

To get some understanding of the potential speed, we measured packet traversal times in our test environment. The first set of measurements, shown in Table 1, focused on the latency of the forwarding node with a very low load. For measurements, we had four different setups, with zero (direct wire) to three NetFPGAs on the path. Packets were sent at the rate of 25 packets/second; both sending and receiving operations were implemented directly in FreeBSD kernel.

The delay caused by the Bloom filter matching code is 64ns (8 clock cycles), which is insignificant compared to the measured  $3\mu s$  delay of the whole NetFPGA processing. With background traffic, the average latency per NetFPGA was increased to  $5\mu s$ .

To get some practical reference, we also compared our implementation with the Stanford reference router. This was quantified by comparing ICMP echo requests' processing times with three setups: using a plain wire,

| Path       | Avg. latency | Std. Dev.  |

|------------|--------------|------------|

| Plain wire | $94 \mu s$   | $28\mu s$  |

| IP router  | $102 \mu s$  | $44 \mu s$ |

| LIPSIN     | $96 \mu s$   | $28\mu s$  |

Table 2: Ping through various implementations

using our implementation, and using the reference IP router with five entries in the forwarding table. To compensate the quite high deviation, caused by sending and receiving ICMP packets and involving user level processing, we averaged over 100 000 samples. Both IP router implementation and our implementation were run on the same NetFPGA hardware. The results are shown in Table 2.

While we did not directly measure the bandwidth due to the lack of test equipment for reliably filling up the pipes, there are no reasons why the implementation would not operate at full bandwidth. To further test this we did send video stream through our implmentation. During the streaming we did send random data through same NetFPGA but with different ports at almost 1Gbs datarate. Both the stream and was forwarded without a problem. The code is straightforward and should be able to keep the pipeline full under all conditions.

IP routers need increasing amount of states, which increases latency and resource consumption, when the size of the network increases. On the other hand, in our implementation, the latency and resource consumption for each node will remain same, independent of the amount of nodes in the network. Because of that, the results we got for one node should remain same even when large amount of nodes are connected to a same network.

### 4.2 **Resource consumption:**

To get an idea how much our implementation consumes resources we did syntetize design with 4 real and 4 virtual LITs per interface. With this configuration, the total usage of NetFPGA resources for the forwarding logic is 4.891 4-input LUTs out of 47.232, and 1.861 Slice Flip/Flops (FF) out of 47.232. No BRAMs are reserved for the forwarding logic. Synthetisizer saves BRAM blocks and uses other logic blocks to create registers for LITs. For the whole system, the corresponding numbers are 20.273 LUTs, 15.347 FFs, and 106 BRAMs. SRAM was used for the output queues in the measured design. We also tested to use BRAMs for output queue and the design works. However, we don't have measurement results from that implementation.

#### 4.3 Forwarding table sizes:

Assuming that each forwarding node maintains d dis-

tinct forwarding tables, each containing an entry per interface, where an entry further consists of a Link ID and the associated output port, we can estimate the amount of memory needed by the forwarding tables:

$FT_{mem} = d \cdot \#Links \cdot [size(LIT) + size(P_{out})] \quad (1)$

Considering d = 8, 128 links (physical & virtual), 248bit LITs and 8 bits for the outport, the total memory required would be 256Kbit, which easily fits on-chip.

Although this memory size is already small, we can design an even more efficient forwarding table by using a *sparse representation* to store just the positions of the bits set to 1. Thereby, the size of each LIT entry is reduced to  $k \cdot log_2(LIT)$  and the total forwarding table requires only  $\approx 48Kbit$  of memory, at the expense of the decoding logic.

## 5. RELATED WORK

OpenFlow [11] [12] provides a platform for experimental switches. It introduces simple, remote controlled, flow based switches, that can be run on existing IP switches. The concept allows evaluation of new ideas and even protocols in Openflow-enabled networks, where the new protocols can be run on top of the IP network. However, as high efficiency is one of our main goals, we wanted to get rid of unnecessary logic and decided for a native zFilter implementation.

There are not yet many publications where NetFPGA is used, in addition to OpenFlow and publications about implementing the NetFPGA card or reference designs. However one technical report were available [10], about implementing flow counter on NetFPGA. Authors of that work used NetFPGA succesfully to demonstrate that their idea can be implemented in practice.

In addition to NetFPGA, there are also other reconfigurable networking hardware approaches. For instance, [9] describes one alternative platform. There are also other platforms that could work for this type of development, for example Combo cards from Liberouter project [1]. However, NetFPGA provides enough speed and resources for our purposes, but Combo cards might become a good option later on if we need higher line speeds.

In the following we briefly discuss some work in the area of forwarding related to our zFilter proposal.

**IP multicast:** Our basic communication scheme is functionally similar to IP-based source specific multicast (SSM) [6], with the IP multicast groups having been replaced by the topic identifiers. The main difference is that we support stateless multicast for sparse subscriber groups, with unicast being a special case of multicast. On the contrary, IP multicast typically creates lots of state in the network if one needs to support a large set of small multicast groups.

Networking applications of Bloom filters:

For locating named resources, BFs have been used to bias random walks in P2P networks [3]. In contentbased pub/sub systems [7], summarized subscriptions are created using BFs and used for event routing purposes. Bloom filters in packet headers were proposed in Icarus [14] to detect routing loops, in [15] for credentialsbased data path authentication, and in [13] to represent AS-level paths of multicast packets in a 800-bit shim header, TREE\_BF. Moreover, the authors of [13] use Bloom filters also to aggregate active multicast groups inside a domain and compactly piggyback this information in BGP updates.

## 6. CONCLUSIONS

Previously, we have proposed a new forwarding fabric for multicast traffic. The idea was based on reversing Bloom filter thinking and placing a Bloom filter into the delivered data packets. Our analysis showed that with reasonably small headers, comparable to those of IPv6, we can handle the large majority of Zipf-distributed multicast groups, up to some 20 subscribers, in realistic metropolitan-sized topologies, without adding any state in the network and with negligible forwarding overhead. For the remainder of traffic, the approach provides the ability to balance between stateless multiple sending and stateful approaches. With the stateful approach, we can handle dense multicast groups with a very good forwarding efficiency. The forwarding decisions are simple, potentially energy efficient, may be parallelized in hardware, and have appealing security properties.

To validate and test those claims, we implemented a prototype of a forwarding node and tested its performance. As described in Chapter 4, we ran some measurements on the forwarding node and concluded that the whole NetFPGA processing for a zFilter creates a  $3\mu s$  delay. This delay could most likely be reduced, because the forwarding operation should take only 64ns (8 clock cycles). Comparison with the IP router implementation was done by using ICMP echo requests, showing zFilter implementation being slightly faster than IP-based forwarding, running on the same NetFPGA platform.

Our simple implementation still lacks some of the advanced features described in [8], for example reverse path creation and signaling. However, it should be quite straightforward to add those features to the existing design. Also, early studies indicate that it should be possible to start adding even more advanced features, like caching, error correction or congestion control to the implementation.

## 7. REFERENCES

- [1] Liberouter. http://www.liberouter.org/.

- [2] B. H. Bloom. Space/time trade-offs in hash coding with allowable errors. *Commun. ACM*,

13(7):422-426, 1970.

- [3] A. Z. Broder and M. Mitzenmacher. Survey: Network applications of Bloom filters: A survey. *Internet Mathematics*, 1:485–509, 2004.

- [4] J. Day. Patterns in Network Architecture: A Return to Fundamentals. Prentice Hall, 2008.

- [5] S. E. Deering and D. Cheriton. Multicast routing in datagram internetworks and extended lans. *ACM Trans. on Comp. Syst.*, 8(2), 1990.

- [6] H. Holbrook and B. Cain. Source-specific multicast for IP. RFC 4607. Aug 2006.

- [7] Z. Jerzak and C. Fetzer. Bloom filter based routing for content-based publish/subscribe. In *DEBS '08*, pages 71–81, New York, NY, USA, 2008. ACM.

- [8] P. Jokela, A. Zahemszky, C. Esteve, S. Arianfar, and P. Nikander. LIPSIN: Line speed publish/subscribe inter-networking. Technical report, www.psirp.org, 2009.

- [9] J. W. Lockwood, N. Naufel, J. S. Turner, and D. E. Taylor. Reprogrammable network packet processing on the field programmable port extender (FPX). In *Proceedings of the 2001* ACM/SIGDA ninth international symposium on Field programmable gate arrays, 2001.

- [10] J. Luo, Y. Lu, and B. Prabhakar. Prototyping counter braids on netfpga. Technical report, 2008.

- [11] N. McKeown, T. Anderson, H. Balakrishnan, G. Parulkar, L. Peterson, J. Rexford, J. Turner, and S. Shenker. Openflow: Enabling innovation in campus networks. In ACM SIGCOMM Computer Communication Review, 2008.

- [12] J. Naous, D. Erickson, G. A. Covington, G. Appenzeller, and N. McKeown. Implementing an openflow switch on the netfpga platform. In Symposium On Architecture For Networking And Communications Systems, 2008.

- [13] S. Ratnasamy, A. Ermolinskiy, and S. Shenker. Revisiting IP multicast. In *Proceedings of ACM SIGCOMM'06*, Pisa, Italy, Sept. 2006.

- [14] A. C. Snoeren. Hash-based IP traceback. In SIGCOMM '01, pages 3–14, New York, NY, USA, 2001. ACM.

- [15] T. Wolf. A credential-based data path architecture for assurable global networking. In *Proc. of IEEE MILCOM*, Orlando, FL, Oct 2007.

- [16] A. Zahemszky, A. Csaszar, P. Nikander, and C. Esteve. Exploring the pubsub routing/forwarding space. In *International* Workshop on the Network of the Future, 2009.

## IP-Lookup with a Blooming Tree Array: A New Lookup Algorithm for High Performance Routers

Gianni Antichi

Andrea Di Pietro

Domenico Ficara gianni.antichi@iet.unipi.it andrea.dipietro@iet.unipi.it domenico.ficara@iet.unipi.it

> Stefano Giordano s.giordano@iet.unipi.it

**Cristian Vairo** cristian.vairo@iet.unipi.it

Gregorio Procissi g.procissi@iet.unipi.it Fabio Vitucci

fabio.vitucci@iet.unipi.it

ABSTRACT

Because of the rapid growth of both traffic and links capacity, the time budget to perform IP address lookup on a packet continues to decrease and lookup tables of routers unceasingly grow. Therefore, new lookup algorithms and new hardware platform are required. This paper presents a new scheme on top of the NetFPGA board which takes advantage of parallel queries made on perfect hash functions. Such functions are built by using a very compact and fast data structure called Blooming Trees, thus allowing the vast majority of memory accesses to involve small and fast onchip memories only.

### Keywords

High Performance, IP Address Lookup, Perfect Hash, Bloom Filters, FPGA

## 1. INTRODUCTION

The primary task of a router is the IP-address lookup: it requires that a router looks, among possibly several thousands of entries, for the best (i.e., the longest) rule that matches the IP destination address of the packet. The explosive growth of Internet traffic and link bandwidth forces network routers to meet harder and harder requirements. Therefore, the search for the Longest Prefix Match (LPM) in the forwarding tables has now become a critical task and it can result often into the bottleneck for high performance routers. For this reason a large variety of algorithms have been presented, trying to improve the efficiency and speed of the lookup.

The algorithm here proposed is based on data structures called Blooming Trees (hereafter BTs) [8], compact and fast techniques for membership queries. A BT is a Bloom Filter based structure, which takes advantage of low false positive probability in order to reduce the mean number of memory accesses. Indeed, the number of required memory accesses is one of the most important evaluation criterion for the quality of an algorithm for high performance routers, given that it

strongly influences the mean time required for a lookup process.

An array of parallel BTs accomplishes the LPM function for the entries of the forwarding table by storing the entries belonging to the 16–32 bit range. Every BT has been configured according to the Minimal Perfect Hash Function (MPHF) [1], a scheme conceived to obtain memory efficient storage and fast item retrieval. Shorter entries, instead, are stored in a very simple Direct Addressing (DA) logical block. DA module uses the address itself (in this case only the 15 most significant bits) as on offset to memory locations.

The implementation platform for this algorithm is the NetFPGA [12] board, a new networking hardware which proves to be a perfect tool for research and experimentation. It is composed of a full programmable Field Programmable Gate Array (FPGA) core, four Gigabit Ethernet ports and four banks of Static and Dynamic Random Access Memories (S/DRAM).

This work is focused on the data-path implementation of the BT-based algorithm for fast IP lookup. The software control plane has been also modified in order to accommodate the management and construction of the novel data structure. The software modifications merges perfectly in the preexistent SCONE (Software Component of the NetFPGA).

The rest of the paper is organized as follows: after the related work in address lookup area, section 3 illustrates the main idea, the overall algorithm and the data structures of our scheme. Then section 4 shows the actual implementation of our algorithm on NetF-PGA while section 5 presents the modifications in the control plane software. Finally, section 6 shows the experimental results and section 7 ends the paper.

#### RELATED WORK 2.

Due to its essential role in Internet routers, IP lookup is a well investigated topic, which encompasses triebased schemes as well as T-CAM solutions and hashing techniques. Many algorithms have been proposed in this area ([4][6][9][10][14][15]); to the best of our knowledge, the most efficient trie-based solutions in terms of memory consumption and lookup speed are Lulea and Tree Bitmap.

Lulea [4] is based on a data structure that can represent large forwarding tables in a very compact form, which is small enough to fit entirely in the L1/L2 cache of a PC Host or in a small memory of a network processor. It requires the prefix trie to be complete, which means that a node with a single child must be expanded to have two children; the children added in this way are always leaf nodes, and they inherit the next-hop information of the closest ancestor with a specified next-hop, or the undefined next hop if no such ancestor exists. In the Lulea algorithm, the expanded unibit prefix trie denoting the IP forwarding table is split into three levels in a 16-8-8 pattern. The Lulea algorithm needs only 4-5 bytes per entry for large forwarding tables and allows for performing several millions full IP routing lookups per second with standard general purpose processors.

Tree Bitmap [6] is amenable to both software and hardware implementations. In this algorithm, all children nodes of a given node are stored contiguously, thus allowing for using just one pointer for all of them; there are two bitmaps per node, one for all the internally stored prefixes and one for the external pointers; the nodes are kept as small as possible to reduce the required memory access size for a given stride (thus, each node has fixed size and only contains an external pointer bitmap, an internal next hop info bitmap, and a single pointer to the block of children nodes); the next hops associated with the internal prefixes kept within each node are stored in a separate array corresponding to such a node. The advantages of Tree Bitmap over Lulea are the single memory reference per node (Lulea requires two accesses) and the guaranteed fast update time (an update of the Lulea table may require the entire table to be almost rewritten).

A hardware solution for the lookup problem is given by CAMs, which minimize the number of memory accesses required to locate an entry. Given an input key, a CAM device compares it against all memory words in parallel; hence, a lookup actually requires one clock cycle only. The widespread use of address aggregation techniques like CIDR requires storing and searching entries with arbitrary prefix lengths. For this reason, T-CAMs have been developed. They could store an additional *Don't Care* state thereby enabling them to retain single clock cycle lookups for arbitrary prefix lengths. This high degree of parallelism comes at the cost of storage density, access time, and power consumption. Moreover TCAMs are expensive and offer little adaptability to new addressing and routing protocols [2].

Therefore, other solutions which use tree traversal

and SRAM-based approach are necessary. For example, the authors of [11] propose a scalable, high-throughput SRAM-based dual linear pipeline architecture for IP Lookup on FPGAs, named DuPI. Using a single Virtex-4, DuPI can support a routing table of up to 228K prefixes. This architecture can also be easily partitioned, so as to use external SRAM to handle even larger routing tables, maintains packet input order, and supports in-place nonblocking route updates.

Other solutions take advantage of hashing techniques for IP lookup. For instance, Dharmapurikar et al. [5] use Bloom Filters (BFs) [3] for longest prefix matching. Each BF represents the set of prefixes of a certain length, and the algorithm performs parallel queries on such filters. The filters return a yes/no match result (with false positives), therefore the final lookup job is completed by a priority encoder and a subsequent search in off-chip hash tables. Instead, in our scheme, we will use BF-like structures which have been properly modified in order to directly provide an index for fast search.

## **3. THE ALGORITHM**

All the algorithms previously described remark the most important metrics to be evaluated in a lookup process: lookup speed, mean number of memory access and update time. Each of the cited solutions tries to maximize general performance, with the aim of be implemented on a high performance router and obtain *line-rate* speed. The main motivations for this work come from the general limitations for high-performance routing hardware: limited memory and speed. Specifically, because of the limited amount of memory available, we adopt a probabilistic approach, thus reducing the number of external memory accesses also.

Because of the large heterogeneity of real IP prefixes distribution (as shown in several works as [5] and [13]), our first idea is to divide the entire rule database into two large groups, in order to optimize the structure:

- the prefixes of length  $\leq 15$ , which are the minority of IP prefixes , are simply stored in a Direct Addressing array; this solution is easily implemented in hardware and requires an extremely low portion of the FPGA logic area;

- the prefixes of length  $\geq 16$  are represented by an array of Blooming Trees (hereafter called BTarray).

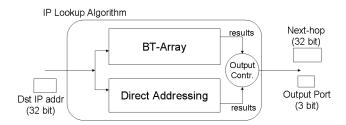

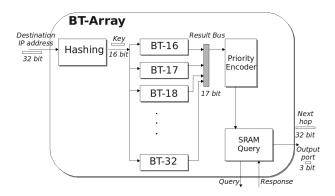

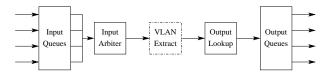

In the lookup process, the destination address under processing is hashed and the output is analyzed by the BT-array and the DA module *in parallel* (see fig. 1). Finally, an *Output Controller* compares the results of both modules and provides the right output (i.e., the longest matching), which is composed of a next-hop ad-

Figure 1: The overall IP lookup scheme.

dress (32 bits) and an output port number (3 bits, given that the NetFPGA has 8 output ports).

In the BT-array the prefixes are divided into groups based on their lengths and every group is organized in an MPHF structure (as shown in fig. 2). Therefore, the BT-array is an array where 17 parallel queries are conducted at the same time; at the end of the process, a bus of 17 wires carries the results: a wire is set to 1 if there is a match in the corresponding filter. Then a priority encoder collects the results of the BT-array and takes the longest matching prefix, while a SRAM query module checks the correctness of the lookup (since BTs are probabilistic filters in which false positives can happen).

Figure 2: BT-array schematic.

#### **3.1 Blooming Tree for MPHF**

The structure we adopt to realize a Minimal Perfect Hashing Functions is a Blooming Tree [8], which is based on the same principles of Bloom Filters and allows for a further memory reduction. The idea of BT is constructing a binary tree upon each element of a plain Bloom Filter, thus creating a multilayered structure where each layer represents a different depth-level of tree nodes.

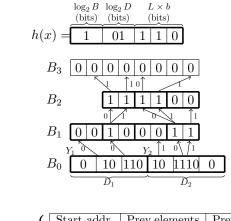

A Blooming Tree is composed of L + 1 layers:

• a plain BF  $(B_0)$  with  $k_0$  hash functions  $h_j$  (j =

$1 \dots k_0$  and *m* bins such that  $m = nk_0/\ln 2$  (in order to minimize the false positive probability);

• L layers  $(B_1 \dots B_L)$ , each composed of  $m_i$   $(i = 1 \dots L)$  blocks of  $2^b$  bits.

Just as a BF,  $k_0$  hash functions are used. Each of them provides an output of  $\log_2 m + L \times b$  bits: the first group of  $\log_2 m$  bits addresses the BF at layer 0, while the other  $L \times b$  bits are used for the upper layers. The lookup for an element  $\sigma$  consists of a check on  $k_0$  elements in the BF (layer 0) and an exploration of the corresponding  $k_0$  "branches" of the Blooming Tree.

"Zero-blocks" (i.e., blocks composed of a string of b zeros which are impossible to be found in a naive BT for construction) are used to stop the "branch" from growing as soon as the absence of a collision is detected in a layer, thus saving memory. This requires additional bitmaps to be used in the construction process only. For more details about BTs, refer to [8].

Our MPHF on BT is based on the statement that, taken the BT as ordering algorithm (with  $k_0=1$ ), a MPHF of an element  $x \in S$  (S is a set of elements) is simply the position of x in the BT:

$$MPHF(x) = position(x) \tag{1}$$

All we need to care when designing this structure is that, in the construction phase, all the collisions vanish, in order to achieve a perfect function.

Instead, as for the lookup, the procedure that finds the position of an element x is divided into two steps:

- find the tree which x belongs to (we call it  $T_x$ ) and compute the number of elements at the  $T_x$ 's left;

- compute the leaves at the left of x in  $T_x$ .

In order to simplify the process, we propose the HSBF [7] as the first level of the BT, instead of the standard BF. The HSBF is composed of a series of bins encoded by Huffman coding, so that a value j translates into j ones and a trailing zero. Therefore, the first step of the procedure is accomplished by a simple popcount in the HSBF of all the bins at the left of x's bin. As for the second step, we have to explore (from left to right) the tree  $T_x$  until we find x, thus obtaining its position within the tree. The sum of these two components gives the hash value to be assigned. For more details about a MPHF realized by means of BT, refer to [1].

A simple example (see fig. 3) clarifies the procedure: we want to compute the MPHF value of the element x. In order to simplify the search in the HSBF, this filter is divided into B sections of D bins, which are addressed through a lookup table. Let us assume B = 2, D = 3, and b = 1: hence, the hash output is 6-bits long.

Let us suppose h(x) = 101110. The first bit is used to address the lookup table: it points to the second entry. We read the starting address of section  $D_2$  and

|              | Start addr. | Prev.elements | Prev. "10" s |

|--------------|-------------|---------------|--------------|

| Lookup Table | $D_1$       | 0             | 0            |

| l            | $D_2$       | 3             | 2            |

Figure 3: Example of hash retrieval through BT.

that 3 elements are in the previous sections (i.e., already assigned by the MPHF). Now we use the next two bits of h(x) to address the proper bin in section  $D_2$ : "01" means the second bin. The popcount on the previous bins in section  $D_2$  indicates that another element is present (so far the total number of elements at  $T_x$ 's left is 4).

Then we focus on  $T_x$ : to move up to the next layer, we both use the third information in the table (the number of '10's in previous sections, which is 2) and count the number of "10"s in the previous bins of this section (that is 1). The sum shows that, before our bin, 3 bins are not equal to 0, so we move to the fourth block in layer  $B_1$ .

Here, the fourth bit of h(x) allows to select the bit to be processed: the second one. But we want to know all the  $T_x$ 's leaves at x's left, hence we have to explore all the branches belonging to the bin under processing. So we start from the first bit of the block and count the number of zero-blocks we find: 2, at layer  $B_3$ . Now the counter reads 6.

Regarding the second bit of the block (which is "the bit of x"), a popcount in layer  $B_1$  indicates the third block in layer  $B_2$ : it is a zero-block, so we have found the block representing our element only: x is the 7-th element in our ordering scheme. Then MPHF(x) = 6.

## 4. IMPLEMENTATION

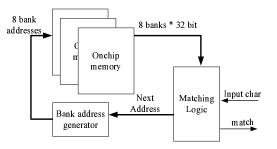

## 4.1 MPHF Module

As above mentioned, the main component of the algorithm is the BT-array, which is composed of a series of MPHFs realized through BTs. Because of the large difficulties in allocating a variable–sized structure in hardware and for the sake of simplicity, in our implementation we simplify the scheme proposed in [1] and adopt a fixed-size structure. In details, the implemented structure presents 3 layers:

- Layer 0: a *Counting Bloom Filter* (CBF) composed of 128 *sections* and with 16 *bins* for every section;

- Layer 1: a simple bitmap that contains *two* bits for every bin of the level 0;

- Layer 2: another bitmap with *two* bits for every bit of the level 1; its size is then of 8192 bits.

These parameters (in terms of number of bins, sections and layers) are chosen in order to allocate, with a very low false positives probability, up to 8192 prefixes per prefix length, which implies that the total maximum number of entries is 128 thousands. Therefore, this implementation can handle even recent prefix rules databases and largely overcome the limitations of the simple (linear-search-based) scheme provided with the standard NetFPGA reference architecture.

Every bin of the CBF, according to the original idea in [1] and as shown in [7], is Huffman–encoded. Again, in order to simplify the hardware implementation, each bin consists of 5 bits and its length is fixed. Thus a maximum of 4 elements are allowed at level 0 for the same bin (i.e.: a trailing zero and max 4 bits set to 1). Since the probability of having bins with more than 4 elements is quite small (around  $10^{-2}$ ) even if the structure is crowded, this implementation allows for a large number of entries to be stored.

Moreover, a lookup table is used to perform the lookup in the layer 0, which is composed of 128 rows containing the SRAM initial address for each section of the CBF. We place the entire BT and the lookup table in the fast BRAM memory: the CBF at layer 0 occupies a block of  $2048 \times 5$  bits, while the lookup table has a BRAM block of  $128 \times 20$  bits.

## 4.2 H3 Hash Function

The characteristics of the hash function to be used in the MPHF are not critical to the performance of the algorithm, therefore a function which ensures a fast hash logic has been implemented: the H3 class of hardware hash functions.

Define A as the key space (i.e. inputs) and B as the address space (i.e. outputs):

- $A = 0, 1, ..., 2^i 1$

- $B = 0, 1, ..., 2^j 1$

where *i* is the number of bits in the key and *j* is the number of bits in the address. The H3 class is defined as follows: denote Q as the set of all the  $i \times j$  boolean matrices. For a given  $q \in Q$  and  $x \in A$ , let q(k) be the

*k*-th row of the matrix *q* and  $x_k$  the *k*-th bit of *x*. The hashing function  $h_q(x) : A \to B$  is defined as:

$$h_q(x) = x_1 \cdot q(1) \oplus x_2 \cdot q(2) \oplus \ldots \oplus x_i \cdot q(i) \quad (2)$$

where  $\cdot$  denotes the binary AND operation and  $\oplus$  denotes the binary exclusive OR operation. The class H3 is the set  $\{h_q | q \in Q\}$ .

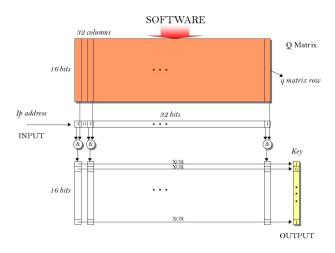

### Figure 4: The scheme of the hash function belonging to the H3 class. The Q matrix is stored in a BRAM block.

Figure 4 shows our H3 design. The process is divided into two steps: first the 32-bit input value (i.e. the IP address) is processed by a block of AND, then the resulting 32 vectors of n bits are XOR-ed by a matrix of logical operations and a resulting string of n bits is provided as output.

The length of the output is chosen to meet the requirements of the following BT-array. The q matrix is pre–programmed via software, passed through the PCI bus, and stored in a BRAM block.

## 4.3 Managing false positives

As already stated, a BT provides also a certain amount of false positives with probability f. Thus every lookup match has to be confirmed with a final lookup into SRAM. Then, intuitively, the average number of SRAM accesses  $\overline{n}$  increases as f grows. More formally, assuming all BTs in the BT-array have the same false positive probability f, we can write:

$$\overline{n} \le 1 + \sum_{i=1}^{16} f^i \le \frac{1}{1-f}$$

(3)

This equation takes into account the probability of the worst case that happens when all BTs provide false positives and are checked in sequence. As one can easily verify, even if f is quite large, the average number of memory accesses is always close to 1 (less than 1.11 for f = 0.1).

## 5. CONTROL PLANE

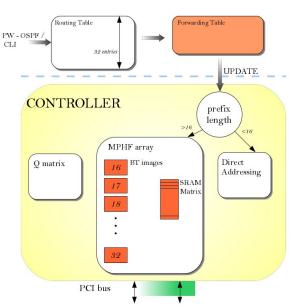

The MPHF IP lookup algorithm needs a controller that manages the building of the database, the setup of the forwarding table, and the potential updates of the prefixes structures. All these functions have been implemented in C/C++ and integrated into the Software SCONE.

SCONE

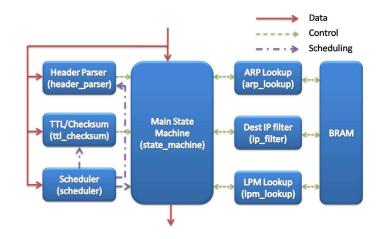

Figure 5: In this figure the different functions of the software control plane can be seen.

This software adopts PW-OSPF as routing protocol, which is a greatly simplified link-state routing protocol based on OSPFv2 (rfc 1247). Every time an update in the routing table occurs, a new forwarding table is created and passed entry by entry through the PCI bus to the NetFPGA. An entry in the forwarding table is composed of destination IP address, subnet mask, gateway, and output port. The original behavior in SCONE was to retransmit all the entries of the forwarding table for each update, while we transmit the modified (new, updated or deleted) entries only. Then the developed Controller analyzes these entries and modifies the proper structures. This communication takes advantage of the register bus.

### 5.1 Updates

When a modification in the forwarding table occurs, it may happen that the new elements lead to collisions in one of the MPHF structures (because they are limited to 2 layers only). In this case, the hash function has to be modified in order to avoid these collisions. This requires the change of the Q matrix and its retransmission to the H3 hashing module, which stores the matrix in a BRAM block. The same communication protocol used for the construction is adopted, indeed a simple registers call has to be made. Therefore, a new hash function is used and all the data-structures for lookup are updated, thus obtaining MHPFs with no collisions.

#### 6. **RESULTS**

In this section, the simulative results about the implementation of our algorithm are shown. In details, we focus on resource utilization, in terms of slices, 4-input LUTs, flip flops, and Block RAMs. We compare our results with those of the NetFPGA reference router where a simple linear search is implemented for IP lookup.

Table 1 shows the device utilization (both as absolute and relative figures) for the original NetFPGA lookup algorithm. It provides a simple lookup table which allows to manage 32 entries only to be looked for through a linear search. Instead we implement a more efficient and scalable algorithm, which is capable of handling up to 130000 entries (by assuming a uniform distribution for entries prefix length). This complexity is obviously paid in terms of resource consumption (see tab. 2): in particular, our lookup module uses 41% of the available slices on the Xilinx Virtex II pro 50 FPGA and 29% of the Block RAMs. However, as for the synthesis of the project, it is worth noticing that even though we use a wide number of resources, the timing closure is achieved without any need to re-iterate the project flow.

Table 1: Resource utilization for the originallookup algorithm.

| Degeumeeg    | XC2VP50           | Utilization |  |  |  |  |

|--------------|-------------------|-------------|--|--|--|--|

| Resources    | Utilization       | Percentage  |  |  |  |  |

| Slices       | 935 out of 23616  | 3%          |  |  |  |  |

| 4-input LUTS | 1321 out of 47232 | 2%          |  |  |  |  |

| Flip Flops   | 343 out of 47232  | 0%          |  |  |  |  |

| Block RAMs   | 3 out of 232      | 1%          |  |  |  |  |

Table 2: Utilization for our algorithm.

| Resources    | XC2VP50            | Utilization |  |  |  |  |

|--------------|--------------------|-------------|--|--|--|--|

| nesources    | Utilization        | Percentage  |  |  |  |  |

| Slices       | 9803 out of 23616  | 41%         |  |  |  |  |

| 4-input LUTS | 10642 out of 47232 | 22%         |  |  |  |  |

| Flip Flops   | 19606 out of 47232 | 41%         |  |  |  |  |

| Block RAMs   | 68 out of 232      | 29%         |  |  |  |  |

Tables 3 and 4 list the specific consumption of the main modules composing our project. In particular, the

Table 3: Utilization for a single MPHF.

| Resources    | XC2VP50            | Utilization |  |  |  |  |  |  |  |  |  |

|--------------|--------------------|-------------|--|--|--|--|--|--|--|--|--|

| Resources    | Utilization        | Percentage  |  |  |  |  |  |  |  |  |  |

| Slices       | 398 out of 23616   | 1%          |  |  |  |  |  |  |  |  |  |

| 4-input LUTS | 561  out of  47232 | 1%          |  |  |  |  |  |  |  |  |  |

| Flip Flops   | 618 out of 47232   | 1%          |  |  |  |  |  |  |  |  |  |

| Block RAMs   | 6 out of 232       | 2%          |  |  |  |  |  |  |  |  |  |

Table 4: Utilization for the hashing module.

|              |                     | _           |  |  |  |  |

|--------------|---------------------|-------------|--|--|--|--|

| Resources    | XC2VP50             | Utilization |  |  |  |  |

| Resources    | Utilization         | Percentage  |  |  |  |  |

| Slices       | 1179 out of 23616   | 4%          |  |  |  |  |

| 4-input LUTS | 1293  out of  47232 | 2%          |  |  |  |  |

| Flip Flops   | 1841 out of 47232   | 3%          |  |  |  |  |

final synthesis summary is reported for both a single MPHF and the hashing module. It is interesting to observe the number of slices required for the hashing compared to that of the table 3: the hashing module ends up to be bigger than the whole MPHF module because of its complexity, since it has to provide 17 different hash values for each of the 17 MPHF blocks.

Finally, table 5 presents the overall device utilization for the reference router including our lookup algorithm and highlights the extensive use of the various resources. In particular we use 94% of the available Block Rams and 74% of slices and LUTs.

#### 7. CONCLUSIONS

This paper presents a novel scheme to perform longest prefix matching for IP lookup in backbone routers. By following the real IP prefixes distributions, we divide the entire rule database into two large groups, in order to optimize our scheme. For prefixes of length < 16, which are the minority of IP prefixes, we use a simple Direct Addressing scheme, while for the others we use an array of Blooming Trees.

The implementation platform for this work is the NetFPGA board, a new networking tool which proves to be very suitable for research and experimentation.

Table 5: Utilization for our overall project.

| Resources     | XC2VP50            | Utilization |

|---------------|--------------------|-------------|

| nesources     | Utilization        | Percentage  |

| Slices        | 17626 out of 23616 | 74%         |

| 4-input LUTS  | 32252 out of 47232 | 74%         |

| Flip Flops    | 31512 out of 47232 | 66%         |

| Block RAMs    | 220 out of 232     | 94%         |

| External IOBs | 360 out of 692     | 52%         |

NetFPGA, originally, provides a simple lookup scheme which allows to manage 32 entries only by means of linear searches. Instead, our scheme is capable of handling up to 130000 entries at the cost of a bigger resource consumption. Anyway, the timing closure is achieved without any need to re-iterate the project flow.

# 8. ADDITIONAL AUTHORS

# 9. REFERENCES

- G. Antichi, D. Ficara, S. Giordano, G. Procissi, and F. Vitucci. Blooming trees for minimal perfect hashing. In *Global Telecommunications Conference, 2008. IEEE GLOBECOM 2008. IEEE*, pages 1–5, 30 2008-Dec. 4 2008.

- [2] F. Baboescu, S. Rajgopal, L. B. Huang, and N. Richardson. Hardware implementation of a tree-based ip lookup algorithm for oc-768 and beyond. In *DesignCon*, 2006.

- [3] B. Bloom. Space/time trade-offs in hash coding with allowable errors. *Communications of the* ACM, 13(7):422–426, July 1970.

- [4] M. Degermark, A. Brodnik, S. Carlsson, and S. Pink. Small forwarding tables for fast routing lookups. In *Proc. of the ACM SIGCOMM '97*, pages 3–14, New York, NY, USA, 1997. ACM.

- [5] S. Dharmapurikar, P. Krishnamurthy, and D. Taylor. Longest prefix matching using bloom filters. In SIGCOMM 2003.

- [6] W. Eatherton, Z. Dittia, and G. Varghese. Tree bitmap: Hardware/software ip lookups with incremental updates. In ACM SIGCOMM Computer Communications Review, 2004.

- [7] D. Ficara, S. Giordano, G. Procissi, and F. Vitucci. Multilayer compressed counting bloom filters. In *Proc. of IEEE INFOCOM '08.*

- [8] D. Ficara, S. Giordano, G. Procissi, and F. Vitucci. Blooming trees: Space-efficient structures for data representation. In *Communications, 2008. ICC '08. IEEE International Conference on*, pages 5828–5832, May 2008.

- [9] P. Gupta and N. Mckeown. Packet classification using hierarchical intelligent cuttings. In *in Hot Interconnects VII*, pages 34–41, 1999.

- [10] T. V. Lakshman and D. Stiliadis. High-speed policy-based packet forwarding using efficient multi-dimensional range matching. In *Proc. of SIGCOMM*, pages 203–214, 1998.

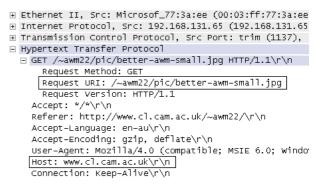

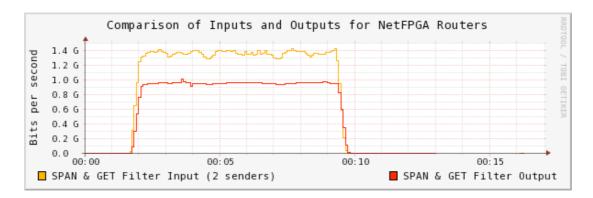

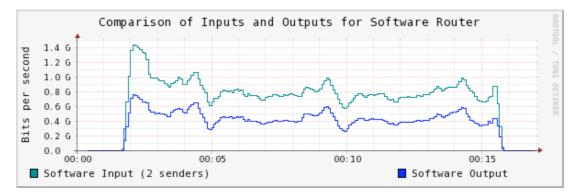

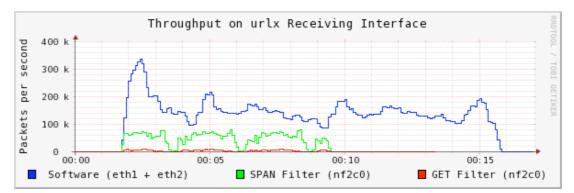

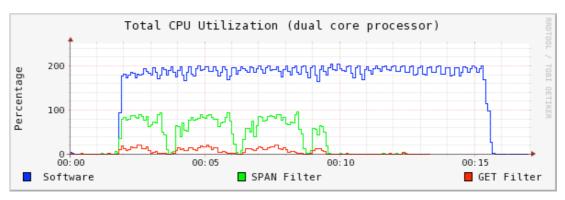

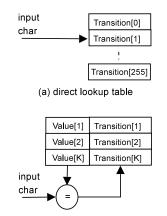

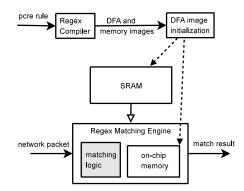

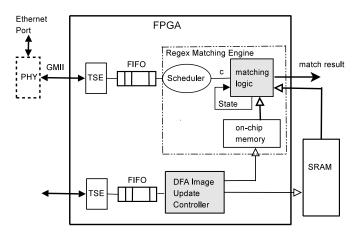

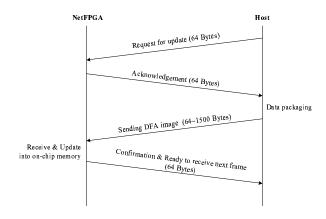

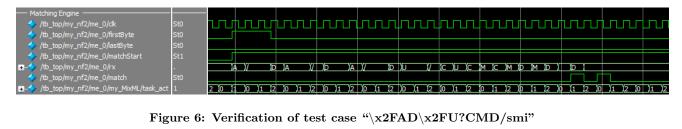

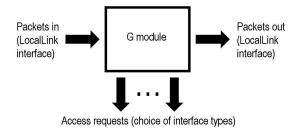

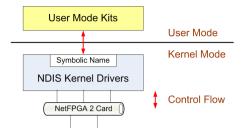

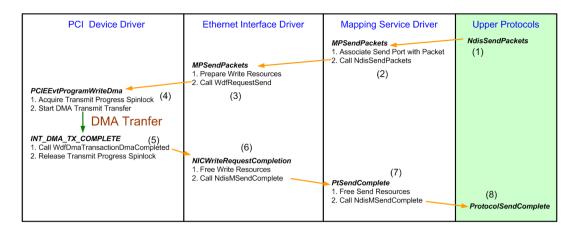

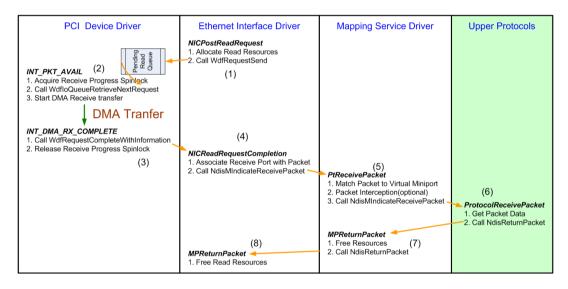

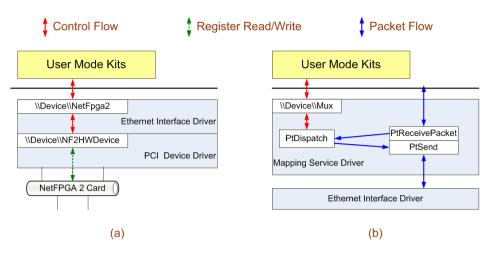

- [11] H. Le, W. Jiang, and V. K. Prasanna. Scalable high-throughput sram-based architecture for ip-lookup using fpga. In *International Conference* on Field Programmable Logic and Applications, 2008.